| Document Title                    | Overview of Functional Safety Measures in AUTOSAR |

|-----------------------------------|---------------------------------------------------|

| Document Owner                    | AUTOSAR                                           |

| Document Responsibility           | AUTOSAR                                           |

| <b>Document Identification No</b> | 664                                               |

| <b>Document Classification</b>    | Auxiliary                                         |

| <b>Document Status</b>  | Final |

|-------------------------|-------|

| Part of AUTOSAR Release | 4.2.2 |

| Document Change History |                                  |                                                                                                                                                                 |

|-------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Release                 | Changed by                       | Change Description                                                                                                                                              |

| 4.2.2                   | AUTOSAR<br>Release<br>Management | <ul> <li>New Chapter: "Hardware Diagnostics" covers<br/>Core Test and RAM Test.</li> <li>Minor corrections / clarifications / editorial<br/>changes.</li> </ul> |

| 4.2.1                   | AUTOSAR<br>Release<br>Management | Initial Release                                                                                                                                                 |

#### **Disclaimer**

This specification and the material contained in it, as released by AUTOSAR, is for the purpose of information only. AUTOSAR and the companies that have contributed to it shall not be liable for any use of the specification.

The material contained in this specification is protected by copyright and other types of Intellectual Property Rights. The commercial exploitation of the material contained in this specification requires a license to such Intellectual Property Rights.

This specification may be utilized or reproduced without any modification, in any form or by any means, for informational purposes only. For any other purpose, no part of the specification may be utilized or reproduced, in any form or by any means, without permission in writing from the publisher.

The AUTOSAR specifications have been developed for automotive applications only. They have neither been developed, nor tested for non-automotive applications.

The word AUTOSAR and the AUTOSAR logo are registered trademarks.

#### Advice for users

AUTOSAR specifications may contain exemplary items (exemplary reference models, "use cases", and/or references to exemplary technical solutions, devices, processes or software).

Any such exemplary items are contained in the specifications for illustration purposes only, and they themselves are not part of the AUTOSAR Standard. Neither their presence in such specifications, nor any later documentation of AUTOSAR conformance of products actually implementing such exemplary items, imply that intellectual property rights covering such exemplary items are licensed under the same rules as applicable to the AUTOSAR Standard.

# **Table of Contents**

| 1 | 1 Introduction                                          | •  |

|---|---------------------------------------------------------|----|

|   | 1.1 Disclaimer                                          | 5  |

|   | 1.2 Scope                                               | 5  |

|   | 1.3 Purpose                                             |    |

|   | 1.4 Intended Audience                                   | 6  |

| 2 | 2 Functional Safety Mechanisms                          |    |

|   | 2.1 Memory Partitioning                                 |    |

|   | 2.1.1 Fault Models                                      |    |

|   | 2.1.2 Description                                       |    |

|   | 2.1.2.1 Application Software                            |    |

|   | 2.1.2.2 OS Applications                                 |    |

|   | 2.1.2.3 Communication and Code Sharing                  |    |

|   | 2.1.2.4 Memory Partitioning within Application Software |    |

|   | 2.1.2.5 Memory Partitioning within Software Components  |    |

|   | 2.1.2.6 Implementation of Memory Partitioning           |    |

|   | 2.1.3 Detection and Reaction                            | 10 |

|   | 2.1.4 Limitations                                       |    |

|   | 2.1.5 References to AUTOSAR Documents                   |    |

|   | 2.1.6 References to ISO26262                            |    |

|   | 2.2 Timing Monitoring                                   |    |

|   | 2.2.1 Fault Models                                      |    |

|   | 2.2.2 Description                                       |    |

|   | 2.2.2.1 Supervised Entities                             |    |

|   | 2.2.2.1 Supervised Entities                             |    |

|   |                                                         |    |

|   | 2.2.2.3 Timing Protection of the Operating System       |    |

|   | 2.2.4 Limitations                                       |    |

|   |                                                         |    |

|   | 2.2.5 References to AUTOSAR Documents                   |    |

|   | 2.2.6 References to ISO26262                            |    |

|   | 2.3 Logical Supervision                                 |    |

|   | 2.3.1 Fault Models                                      |    |

|   | 2.3.2 Description                                       |    |

|   | 2.3.3 Detection and Reaction                            |    |

|   | 2.3.4 Limitations                                       |    |

|   | 2.3.5 References to AUTOSAR Documents                   |    |

|   | 2.3.6 References to ISO26262                            |    |

|   | 2.4 End-2-End Protection                                |    |

|   | 2.4.1 Fault Models                                      |    |

|   | 2.4.2 Description                                       |    |

|   | 2.4.2.1 End-2-End Profiles                              |    |

|   | 2.4.2.2 End-2-End State Machine                         |    |

|   | 2.4.2.3 Integration of the End-2-End Protection Library |    |

|   | 2.4.2.4 End-2-End Protection Wrapper                    |    |

|   | 2.4.2.5 Transmission Manager                            |    |

|   | 2.4.2.6 COM End-2-End Callout                           |    |

|   | 2.4.2.7 RTE Data Transformer                            |    |

|   | 2.4.3 Detection and Reaction                            |    |

|   | 2.4.4 Limitations                                       | 52 |

# Overview of Functional Safety Measures in AUTOSAR

# AUTOSAR Release 4.2.2

|   | 2.4.  | .5 References to AUTOSAR Documents                     | 53 |

|---|-------|--------------------------------------------------------|----|

|   | 2.4.0 | .6 References to ISO26262                              | 55 |

| 3 | Fun   | nctional Safety Measures                               | 56 |

|   | 3.1   | Functional Safety Measures of AUTOSAR                  | 56 |

|   | 3.2   | Traceability                                           | 57 |

|   | 3.3   | Development Measures and the Evolution of the Standard | 57 |

|   | 3.4   | Functional Safety Measures not delivered by AUTOSAR    | 59 |

|   | 3.5   | Safety related Extensions of Methodology and Templates | 60 |

|   | 3.6   | Safety Use Case                                        | 60 |

| 4 | Hard  | dware Diagnostics                                      | 61 |

|   | 4.1   | Core Test                                              | 61 |

|   | 4.1.  | .1 Fault Models                                        | 61 |

|   | 4.1.  | .2 Description                                         | 62 |

|   | 4.1.  | .3 Detection and Reaction                              | 62 |

|   | 4.1.4 |                                                        |    |

|   | 4.1.  | .5 References to AUTOSAR Documents                     | 63 |

|   | 4.1.0 | .6 References to ISO26262                              | 66 |

|   | 4.2   | RAM Test                                               | 66 |

|   | 4.2.  | .1 Fault Models                                        | 66 |

|   | 4.2.2 | .2 Description                                         | 67 |

|   | 4.2.  | .3 Detection and Reaction                              | 67 |

|   | 4.2.  |                                                        |    |

|   | 4.2.  | .5 References to AUTOSAR Documents                     | 68 |

|   | 4.2.0 | .6 References to ISO26262                              | 69 |

| 5 | App   | pendix                                                 | 70 |

|   | 5.1   | Acronyms and abbreviations                             | 70 |

|   | 5.2   | Related Documents                                      | 71 |

|   |       |                                                        |    |

### 1 Introduction

Functional safety is a system characteristic which is taken into account from the beginning, as it may influence system design decisions. Therefore AUTOSAR specifications include requirements related to functional safety.

Aspects such as complexity of the system design can be relevant for the achievement of functional safety in the automotive field.

Software is one parameter that can influence complexity on system level. New techniques and concepts for software development can be used in order to minimize complexity and therefore can ease the achievement of functional safety.

AUTOSAR supports the development of safety-related systems by offering safety measures and mechanisms. However AUTOSAR is not a complete safe solution.

The use of AUTOSAR does not imply ISO26262 compliance. It is still possible to build unsafe systems using the AUTOSAR safety measures and mechanisms.

#### 1.1 Disclaimer

This explanatory document represents the functional safety measures and mechanisms of the latest release of AUTOSAR. Some of the described mechanisms and measures may be implemented differently or may not be available in previous releases. The user of this document shall always consult the applicable referenced documents.

## 1.2 Scope

The content of this document is structured into separate chapters as follows:

Functional Safety Mechanisms: This chapter contains AUTOSAR functional safety mechanisms related to freedom from interference between AUTOSAR SW-Cs.

- Memory: Partitioning mechanisms of AUTOSAR with the context of Application Software development and deployment.

- Timing: Temporal Program Flow Monitoring mechanisms using the Watchdog Manager and Timing Protection mechanisms using the Operating System.

- Execution: Logical Supervision mechanisms using the Watchdog Manager.

- Exchange of Information: Communication fault detection mechanisms using the End-2-End Library and Extensions.

Functional Safety Measures: This chapter contains topics related to the development of safety-relevant systems. The following items are covered:

- Functional Safety Measures of AUTOSAR, such as Traceability, Development Measures and the Evolution of the Standard.

- Functional Safety Measures not delivered by AUTOSAR.

- Safety Use Case: An exemplary safety related system using AUTOSAR based on the guided tour example Front Light Management.

• Safety Extensions: How safety requirements can be expressed within the AUTOSAR models and documents by means of the AUTOSAR meta-model.

Hardware Diagnostics: This chapter contains topics related to the premise, that the provided functionality of the microcontroller can be trusted. The following items are covered:

- Core Test.

- RAM Test.

### 1.3 Purpose

Information about AUTOSAR functional safety mechanisms and measures is currently distributed throughout the referenced documentation. Unless one knows how functional safety mechanisms are supported and where the necessary information is specifically located, it is difficult to evaluate how a safety-relevant system can be implemented using AUTOSAR efficiently.

This explanatory document summarizes the key points related to functional safety in AUTOSAR and explains how the functional safety mechanisms and measures can be used.

Note: This document supersedes the AUTOSAR document "Technical Safety Concept Status Report", ID: 233.

#### 1.4 Intended Audience

This document gives an overview of the functional safety measures and mechanisms of AUTOSAR and their implementation to those involved in the development of safety-relevant (ECU) systems. Therefore this document is intended for the users of AUTOSAR, including people involved in safety analysis.

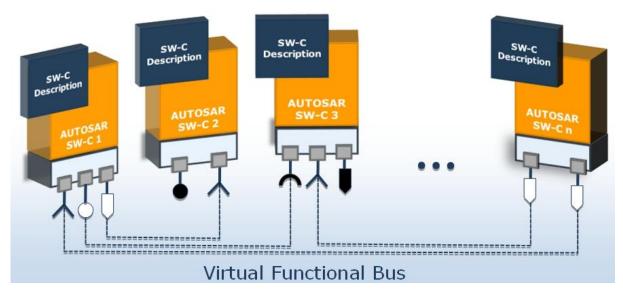

# 2 Functional Safety Mechanisms

Modern ECUs contain highly modular embedded software, which can consist of both non-safety-related and safety-related software components, which perform functions with different ASIL ratings.

According to ISO 26262<sup>1</sup>, if the embedded software consists of software components with different ASIL ratings, then either the entire software must be developed according to the highest ASIL, or freedom from interference shall be ensured for software components with a higher ASIL rating from elements with a lower ASIL rating.

Furthermore, the ISO 26262<sup>2</sup> standard provides examples for faults, which cause interference between software components. The faults are grouped as follows:

- Memory

- Timing

- Execution

- Exchange of Information

During the course of the following chapter, an overview of AUTOSAR functional safety mechanisms<sup>3</sup> is given. Those mechanisms assist with the prevention, detection and mitigation of hardware and software faults to ensure freedom from interference between software components.

Note: AUTOSAR functional safety mechanisms are used to support the development of safety-related systems. Therefore, functional safety mechanisms (software and hardware) are safety-related and must be developed and integrated accordingly.

1

<sup>&</sup>lt;sup>1</sup> [ISO 26262-6 7.4.10]

<sup>&</sup>lt;sup>2</sup> [ISO 26262-6, Annex D] Freedom from interference between software elements.

<sup>&</sup>lt;sup>3</sup> In the context of this document, functional safety mechanisms are a concrete product part, such as memory protection. They are considered as specialization of functional safety measures, which also include process steps, like a review. This definition is in line with the definition given in ISO 26262 for these terms.

## 2.1 Memory Partitioning

A modular implementation of embedded systems that consists of both safety-related software components of different ASILs or of safety-related and non-safety-related software components is facilitated by AUTOSAR features that support freedom from interference between such software components.

Software Components which are developed according to a low ASIL rating may interfere by wrongfully accessing memory regions of software components with a higher ASIL rating. An execution of software components in separate memory regions or memory partitions supports the prevention of such memory access violations. Please see section 2.1.2.6 for further details.

The features described in this chapter are part of the OS and the RTE functionality, which are required to enable groups of SW-Cs to run in separate memory partitions, in order to provide freedom from interference between software components.

#### 2.1.1 Fault Models

According to ISO 26262<sup>4</sup>, the following memory-related effects of faults can be considered as a cause for interference between software components:

- Corruption of content.

- Read or write access to memory allocated to another software element.

The functional safety mechanism Memory Partitioning provides protection by means of restricting access to memory and memory-mapped hardware. Memory partitioning means that OS-Applications reside in different memory areas (partitions) that are protected from each other. In particular, code executing in one partition cannot modify memory of a different partition. Moreover, memory partitioning enables to protect read-only memory segments (e.g. code execution), as well as to protect memory-mapped hardware.

The memory partitioning and user/supervisor-modes related features address the following goal: Supporting freedom from interference between software components by means of memory partitioning (e.g. memory-related faults in SW-Cs do not propagate to other software modules and SW-Cs executed in user-mode have restricted access to CPU instructions like e.g. reconfiguration).

<sup>&</sup>lt;sup>4</sup> [ISO 26262-6, Annex D] D.2.3 Memory

#### 2.1.2 Description

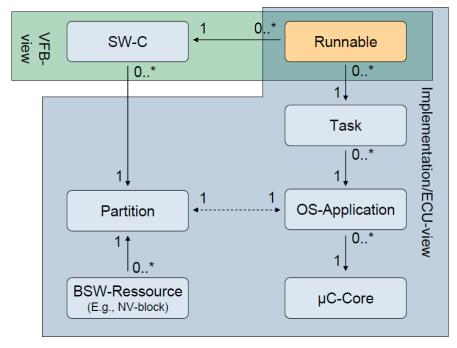

Memory Partitioning is an extension of the RTE and the OS, which is described in the AUTOSAR Specification as "One Partition will be implemented using one OS-Application" and "SW-Cs grouped in separate user-mode memory partitions". During the course of this chapter, this extension will be described as the relationship of Runnables, Tasks, Software Components and OS-Applications in the context of the AUTOSAR Methodology.

#### 2.1.2.1 Application Software

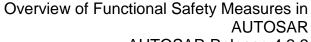

In the AUTOSAR Architecture, Application Software is located above the RTE and consists of interconnected AUTOSAR Software Components, which atomically encapsulate parts of the Application Software functionality.

Figure 1: Application Software

AUTOSAR Software Components are hardware-independent, so they can be integrated onto any available ECU Hardware. To facilitate the inter- and intra-ECU information exchange, AUTOSAR Software Components communicate exclusively over the RTE.

AUTOSAR Software Components contain a number of Functions and Variables, which provide the internal functionality. The internal structure of an AUTOSAR Software Component, its Variables and Function Calls, is hidden from the public view via the header files. Only the external RTE calls are presented at the public interface.

9 of 71

<sup>&</sup>lt;sup>5</sup> Specification of ECU Configuration, V3.5.0, R4.1 Rev 3, Page 154, ECUC\_EcuC\_00005

<sup>&</sup>lt;sup>6</sup> Requirements on AUTOSAR Features, V1.2.1, R4.1 Rev 2, Chapter 4.11 Safety

**AUTOSAR Release 4.2.2**

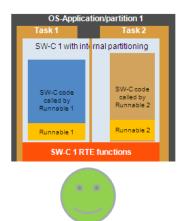

**Figure 2: Software Components**

AUTOSAR Software Components also contain functions, which must be invoked at runtime. Those C-functions are referred to as Runnables in AUTOSAR.

Runnables cannot be executed by themselves; they must be assigned to executable entities of the operating system. Such an assignment can be performed by inserting function calls of Runnables into OS-Task bodies.

Runnables are then executed cyclically and/or event-driven in the context of their caller OS-Task. The assignment of Runnables to Tasks is performed according to Figure 3 and Figure 4.

Figure 3: AUTOSAR Layered Software Architecture - Mapping of Runnables<sup>7</sup>

<sup>&</sup>lt;sup>7</sup> Layered Software Architecture, V3.4.0, R4.1 Rev 3, Page 105

10 of 71 Document ID 664: AUTOSAR TR Ove

#### 2.1.2.2 OS Applications

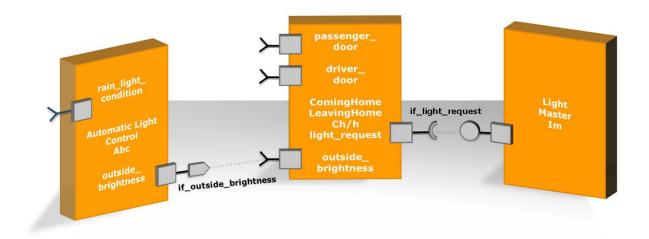

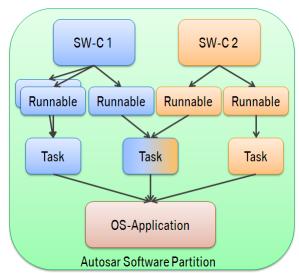

Figure 4 presents an interpretation of the relations from Figure 3. Runnables from AUTOSAR Software Components are assigned to OS-Tasks according to this diagram.

Figure 4: Mapping of Software Components to OS-Applications

AUTOSAR OS-Applications are collections of Operating System objects such as Tasks, ISRs, Schedule Tables, Counters and Alarms that form a cohesive functional unit. All objects which belong to the same OS-Application have access to each other.

The Operating System objects within an OS-Application may belong to different AUTOSAR Software Components. The RTE implements a memory area which is accessible by all members of the OS-Application without restrictions to facilitate communication between the SW-Cs efficiently.

There are two classes of OS-Applications:

- "Trusted OS-Applications are allowed to run with monitoring or protection features disabled at runtime. They may have unrestricted access to memory and the Operating System module's API. Trusted OS-Applications need not have their timing behavior enforced at runtime. They are allowed to run in privileged mode when supported by the processor."

- 2. "Non-Trusted OS-Applications are not allowed to run with monitoring or protection features disabled at runtime. They have restricted access to memory, restricted access to the Operating System module's API and have their timing behaviour enforced at runtime. They are not allowed to run in privileged mode when supported by the processor."

11 of 71

$<sup>^{8}</sup>$  Specification of Operating System, V5.3.0 R4.1 Rev 3, Chapter 7.6.1

#### 2.1.2.3 Communication and Code Sharing

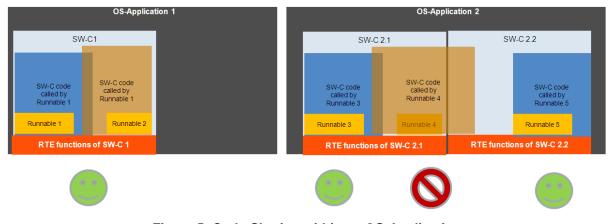

According to Figure 4 and Figure 3, an OS-Application can contain multiple AUTOSAR Software Components and associated Runnables. Runnables are only allowed to directly access variables and to perform function calls within their respective Software Component.

Internal Function Calls and Variables of a Software Component are not publically known by other Software Components, as their definitions are not presented by the header files of the external interface.

Therefore, a direct communication via variables and the execution of Code of other Software Components is not intended.

In Figure 5, this is illustrated by the example of code-sharing, which is only allowed within the Software Component and not between Software Components of one OS-Application. Communication with other Software Components shall be performed via the RTE. Runnable 4 may not execute functions belonging to SW-C 2.2.

Figure 5: Code-Sharing within an OS-Application

#### 2.1.2.4 Memory Partitioning within Application Software

Application Software in an AUTOSAR ECU can consist of safety-related and non-safety-related Software Components. Freedom from interference between Software Components with different ASIL ratings shall be ensured according to the requirements of ISO 26262<sup>9</sup>.

The AUTOSAR Operating System provides freedom from interference for memory-related faults by placing OS-Applications into separate memory regions. This mechanism is called Memory Partitioning. OS-Applications are protected from each other, as code executing in the Memory Partition of one OS-Application cannot modify other memory regions. The corresponding requirements from the AUTOSAR OS specification are presented in Table 1.

| Req. ID  | Requirement Text                                                       |

|----------|------------------------------------------------------------------------|

| [SWS_Os_ | The Operating System module shall prevent write access to the OS-      |

| 00207]   | Application's private data sections from other non-trusted OS-         |

|          | Applications.                                                          |

| [SWS_Os_ | The Operating System module shall prevent write access to all private  |

| 00355]   | stacks of Tasks/Category 2 ISRs of an OS-Application from other non-   |

|          | trusted OS-Applications.                                               |

| [SWS_Os_ |                                                                        |

| 00356]   | data sections of a Task/Category 2 ISR of an OS-Application from other |

|          | non-trusted OS-Applications.                                           |

Table 1: AUTOSAR OS - Memory Partitioning for OS-Applications<sup>10</sup>

Application Software can consist of Software Components with different ASIL ratings. However, Software Components with different ASIL ratings should not be assigned to the same OS-Application. Memory Partitioning does not provide freedom from interference between Software Components which are assigned to the same OS-Application. The Operating System only prevents other OS-Applications from performing improper accesses. A faulty Software Component would not be prevented from modifying memory areas of other Software Components within the same OS-Application.

Note: Please consult the subsequent section for details on Task-level partitioning.

\_

<sup>&</sup>lt;sup>9 9</sup> [ISO 26262-6 7.4.10]

<sup>&</sup>lt;sup>10</sup> Specification of Operating System, V5.3.0 R4.1 Rev 3

#### 2.1.2.5 Memory Partitioning within Software Components

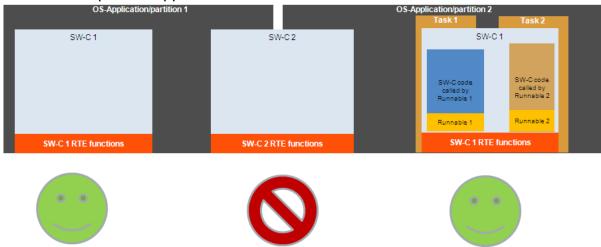

A Mixed-ASIL Software Component could consist of Runnables with different ASIL ratings and therefore requires an execution environment which supports freedom from interference between those Runnables. An execution of different Runnables of one Software Component in different Memory Partitions is not possible due to the following:

Memory Partitioning is performed at the level of OS-Applications. According to Figure 3 and Figure 4 however, a Software Component can only be assigned to one OS-Application and therefore has only one Memory Partition. Also, Runnables of a Software Component can only be called by the Tasks of one OS-Application.

As shown in Figure 6, Runnables of a Software Component cannot be distributed to Tasks of multiple OS-Applications.

Figure 6: SWCs vs. Partitions

Memory Partitioning cannot be used to separate Runnables within the same SW-C. If it is necessary to have a Software Component comprise Runnables with different ASIL-ratings and an independent execution with freedom from interference is required for those Runnables, then memory partitioning at OS-Application level is not sufficient, memory partitioning has to be performed at Task-level. This approach is shown in Figure 7.

Figure 7: Task Partitioning

Requirements related to Memory Partitioning at Task-level are listed in the AUTOSAR OS specification in Table 2. The use of the weak word "may" shows that an implementation of Task-level partitioning is optional for the AUTOSAR OS. Therefore, not every AUTOSAR OS implementation may support Task-level Memory Partitioning.

| Req. ID  | Requirement Text                                                     |

|----------|----------------------------------------------------------------------|

| [SWS_Os_ | The Operating System module may prevent write access to the private  |

| 00208]   | stack of Tasks/Category 2 ISRs of a non-trusted application from all |

|          | other Tasks/ISRs in the same OS-Application.                         |

| [SWS_Os_ | The Operating System module may prevent write access to the private  |

| 00195]   | data sections of a Task/Category 2 ISR of a non-trusted application  |

|          | from all other Tasks/ISRs in the same OS-Application.                |

Table 2: AUTOSAR OS Requirements – Memory Partitioning for Tasks<sup>11</sup>

<sup>11</sup> Specification of Operating System, V5.3.0 R4.1 Rev 3

#### 2.1.2.6 Implementation of Memory Partitioning

A broad variety of technical safety concepts on the system- and software level can be implemented using the mechanism Memory Partitioning.

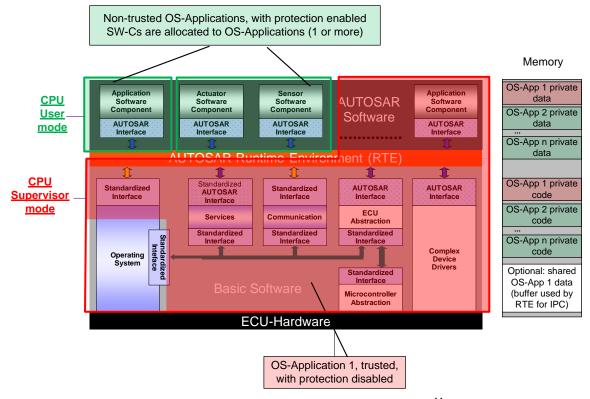

Figure 8 shows a possible implementation whereas all Basic Software Modules are executed in one trusted/supervisor-mode<sup>12</sup> memory partition (highlighted in red in Figure 8). Some SW-Cs are logically grouped and put in separate non- trusted/user-mode memory partitions (highlighted in green). Selected SW-Cs belong to the same trusted/supervisor-mode memory partition as the Basic Software Modules (see fourth SW-C in Figure 8 highlighted in red). There may be several non-trusted/user-mode<sup>13</sup> partitions, each containing one or more SW-Cs.

Figure 8: Memory partitioning and modes<sup>14</sup>

The execution of SW-Cs in non-trusted/user-mode memory partitions is restricted from modifying other memory regions, whereas the execution of SW-Cs of trusted/supervisor-mode memory partitions is not restricted.

Modern microcontrollers for safety relevant applications support memory partitioning via dedicated hardware, a Memory Protection Unit (MPU).

16 of 71

<sup>&</sup>lt;sup>12</sup> Supervisor Mode, Privileged Mode and Elevated Mode are synonyms for the elevated CPU mode. Trusted Mode is a mode of the Software, which is executed under the elevated CPU Mode.

<sup>&</sup>lt;sup>13</sup> User Mode and Non-Privileged Mode are synonyms for a non-elevated CPU mode. Non-Trusted Mode is a mode of the Software, which is executed under the non-elevated CPU Mode.

<sup>&</sup>lt;sup>14</sup> Technical Safety Concept Status Report, V1.2.0, R4.1 Rev 1, Chapter 1.1.6 Memory Partitioning and User/Supervisor-Modes Related Features

Note: It is assumed that memory partitioning will be implemented on a microcontroller which has an MPU or similar hardware features<sup>15</sup>.

With a typical MPU implementation, access to multiple sections of the microcontroller address space can be allowed for non-trusted applications. Access control is defined as a combination of Read, Write and Execute accesses. The configuration of the MPU is only permissible in supervisor mode.

Note: In some microcontroller implementations the MPU is integrated within the Processor Core. Therefore that MPU only controls accesses of the associated Core. Other Bus Masters, such as DMA controllers and additional Cores, are not controlled by this particular MPU instance.

The following table and use cases illustrate a set of possible scenarios when the configuration of the memory protection unit is derived from system requirements. Note: This table may be incomplete with respect to the features of the specific hardware devices in use.

| Address<br>Space | Rationale                                                                                                                                                                                                                                                                                                                                                    | Read | Write | Execute |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------|

| Flash Memory     | Read, Execute and Write accesses do not modify flash memory contents. Flash memory must be erased and enabled for writing by a different mechanism first.  Note: The following implications arise from the Security point of view: Reading and execution of foreign code may be used to obtain information which is otherwise not intended for the software. | O    | O     | O       |

| RAM              | Write access to RAM may produce memory corruptions, thereby affecting the behavior of the software.                                                                                                                                                                                                                                                          | 0    | X     | 0       |

| Peripheral       | Side effects are possible even when reading from peripheral address space. E.g.: Acknowledgement of an Interrupt is performed via a read access to the Interrupt Controller, Read access to peripherals may cause I/O errors.                                                                                                                                | X    | X     | X       |

Table 3: Configuration scenarios for Memory Protection

#### Legend:

X – Protection is needed

O – Protection is optional

Note: Side effects from performance point of view may arise due to Bus Contention, arbitration at interfaces, etc.

<sup>&</sup>lt;sup>15</sup> [ISO26262-6 7.4.11 b)] 17 of 71

# Overview of Functional Safety Measures in AUTOSAR AUTOSAR Release 4.2.2

Use Case 1: Software Components in the same Partition.

- Software Components in the same partition have access to each other's RAM regions, and therefore can corrupt each other's memory contents.

- Software components do not have access to peripheral devices by definition, as they shall be not aware of the underlying microcontroller architecture. An unsafe system can be created when a software component is given direct access to peripheral devices.

Use Case 2: Software Components in different Partitions.

- Software Components in different partitions do not have access to each other's RAM regions, and therefore cannot corrupt each other's memory contents.

- Software components do not have access to peripheral devices by definition, as they shall be not aware of the underlying microcontroller architecture. A potentially unsafe system can be created when a software component is given direct access to peripheral devices.

#### Use Case 3: MCAL Drivers

- MCAL Drivers are a collection of functions, such as Read/Write/Initialize. They

must be executed by another entity, such as the BSW or a CDD. Please see

Figure 8 for details.

- MCAL Drivers need a Read/Write access to the peripheral space of the respective peripheral hardware module. Depending on the hardware architecture, supervisor mode of the processor may be additionally required.

#### 2.1.3 Detection and Reaction

The functional safety mechanism Memory Partitioning provides protection by means of restricting access to memory and memory-mapped hardware. Code executing in one partition cannot modify memory of a different partition. Memory partitioning enables to protect read-only memory segments, as well as to protect memorymapped hardware. Moreover, Software Components which are executed in usermode have restricted access to CPU instructions like e.g. reconfiguration.

The mechanism Memory Partitioning can be implemented with the support of microcontroller hardware such as Memory Protection Unit or Memory Management Unit. The microcontroller hardware must be configured appropriately by the Operating System to facilitate detection and prevention of incorrect memory accesses. The execution of Software Components which are executed in nontrusted/user-mode memory partitions is then monitored.

In case of a memory access violation or a CPU instruction violation in a nontrusted/user-mode partition, the faulty access is blocked and an exception is raised by the microcontroller hardware. The OS and the RTE handle the erroneous software partition by performing either a partition shut down or restart of all SW-Cs of this partition.

Note: The actual reaction of the Operating System can be configured though the Protection Hook implementation. Please consult the OS SWS<sup>16</sup> document for further details.

Note: The AUTOSAR Document "Explanation of Error Handling on Application Level"<sup>17</sup> provides additional information on error handling. Within the document it is explained how error handling can be performed and where the required data (e.g. substitute values) can be obtained from. Furthermore the document provides a detailed explanation (user's manual) on how OS-Application/Partition termination and restart in AUTOSAR is performed.

<sup>17</sup> Explanation of Error Handling on Application Level, R4.2 Rev 1, Chapter 8, Chapter 10

<sup>&</sup>lt;sup>16</sup> Specification of Operating System, V5.3.0 R4.1 Rev 3

#### 2.1.4 Limitations

1. Memory Partitioning of SW-Cs with the same ASIL rating.

The ISO26262<sup>18</sup> standard requires freedom from interference between Software Components of different ASIL ratings. However, freedom from interference between Software Components of the same ASIL rating is not required by the standard.

OS-Applications which consist of a large number of Software Components are allowed. In case a single Software Component causes a violation which results in shutdown or restart of the entire memory partition, all other correctly working SW-Cs of this memory partition are affected as well.

- 2. Memory Partitioning is not applicable for trusted OS-Applications. The execution of trusted/supervisor-mode memory partitions is not controlled by means of the Operating System and some MMU/MPU hardware implementations.

- 3. Memory Partitioning not supported on task-level. The implementation of task-level partitioning is not mandatory for AUTOSAR OS implementations. Freedom from Interference within the OS-Application may be therefore not supported.

- 4. Performance penalty due to Memory Partitioning. Depending on the architecture of the Application Software and the implementation of microcontroller hardware and the OS, there is a performance penalty associated with the use of Memory Partitioning. This penalty increases with the number of context switches which are performed per time unit.

- 5. No Basic Software Partitioning.

The current specification of the Basic Software does not specify memory partitioning for Basic Software Components with different ASIL ratings from different suppliers.

18 [ISO 26262-9 Clause 6] 20 of 71

#### 2.1.5 References to AUTOSAR Documents

**Source:** Requirements on AUTOSAR Features, V1.2.1, R4.1 Rev 2

# [RS\_BRF\_01232] AUTOSAR OS shall support isolation and protection of application software

| _                    |                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:                | Valid                                                                                                                                                                                                                                                                                                                                                      |

| Description:         | AUTOSAR OS shall support to organize all objects handled by<br>the OS such that they can be assigned to different entities<br>(OSApplications) and that access between OSApplications is<br>restricted. This includes usage of hardware memory protection.<br>Note: Assignment of Software Components to OSApplications<br>needs to be done outside the OS |

| Rationale:           | This is a pre-requirement to install protection mechanisms for higher level BSW and Software Components                                                                                                                                                                                                                                                    |

| Use Case:            | Usage of memory protection properties of microcontrollers to catch erroneous write access of software components                                                                                                                                                                                                                                           |

| Dependencies:        |                                                                                                                                                                                                                                                                                                                                                            |

| Supporting Material: |                                                                                                                                                                                                                                                                                                                                                            |

<sup>| (</sup>RS\_Main\_00010, RS\_Main\_00100)

# [RS\_BRF\_02048] AUTOSAR shall support usage of hardware memory protection features to enhance safety

| Туре:                | Valid                                                                                                                                                                                                                                      |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description:         | If adequate memory protection mechanisms are supported by hardware, AUTOSAR shall support the usage of these hardware mechanisms in such a way that memory used by SW-Cs and BSW modules can be protected from illegal or erroneous access |  |

| Rationale:           | Only if it can be shown that different groups of software components do not interfere, the groups of software components can be evaluated separately with respect to their safety requirements                                             |  |

| Use Case:            | Combine software components of different ASIL level on the same ECU                                                                                                                                                                        |  |

| Dependencies:        |                                                                                                                                                                                                                                            |  |

| Supporting Material: | ISO 26262-6:2011, Annex D (Freedom from interference between software elements)                                                                                                                                                            |  |

J (RS\_Main\_00010)

# [RS\_BRF\_01248] AUTOSAR OS shall support to terminate and restart OSApplications

| Type:                | Valid                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description:         | AUTOSAR OS shall support to terminate and – if wanted - restart OSApplications                                                                                                                                                                                                        |

| Rationale:           | If an OSApplication encounters an error, the error strategy of<br>the ECU needs to decide if this OSApplication can be permitted<br>to continue working, and eventually terminate or terminate and<br>restart the OSApplication. The OS needs to offer the necessary<br>functionality |

| Use Case:            | Memory protection error in an OSApplication which cannot be salvaged without terminating the OSApplication                                                                                                                                                                            |

| Dependencies:        |                                                                                                                                                                                                                                                                                       |

| Supporting Material: |                                                                                                                                                                                                                                                                                       |

| (RS\_Main\_00010, RS\_Main\_00100)

#### 2.1.6 References to ISO26262

The following references to the ISO26262 standard are related to the aspects of freedom from interference for software components with different ASIL ratings. Additionally, concepts related to software partitioning and memory-related faults are covered.

|    | <del></del>        |

|----|--------------------|

| ID | ISO26262 Reference |

| 01 | Part 6: [7.4.11]   |

| 02 | Part 6: [7.4.12]   |

| 03 | Part 6: [D.2.1]    |

| 04 | Part 6: [D.2.3]    |

| 05 | Part 9: [6.2]      |

| 06 | Part 9: [6.4.4]    |

| 07 | Part 9: [6.4.5]    |

**Table 4: ISO26262 Memory Partitioning References**

# 2.2 Timing Monitoring

Timing is an important property of embedded systems. Safe behavior requires that the systems actions and reactions are performed within the right time.

The right time can be described in terms of a set of timing constraints that have to be satisfied. However, an AUTOSAR software component cannot ensure proper timing by itself. It depends on proper support by the AUTOSAR runtime environment and the basic software. During integration the timing constraints of the AUTOSAR software components need to be ensured.

#### 2.2.1 Fault Models

According to ISO 26262<sup>19</sup>, the following Timing- and Execution-related faults can be considered as a cause for interference between software components:

- Blocking of execution

- Deadlocks

- Livelocks

- Incorrect allocation of execution time

- Incorrect synchronization between software elements

Timing protection and monitoring can be described as monitoring of the following properties: Monitoring that tasks are dispatched at the specified time, meet their execution time budgets, and do not monopolize OS resources.

To guarantee that safety-related functions will respect their timing constraints, tasks monopolizing the CPU (such as heavy CPU load, many interrupt requests) shall be detected and handled.

24 of 71

#### 2.2.2 Description

The following timing monitoring mechanisms are provided by AUTOSAR:

- 1. Timing Protection mechanisms using the Operating System.

- 2. Temporal Program Flow Monitoring using the Watchdog Manager.

This chapter will explain the applicability of the Watchdog Manager for implementing timing monitoring of Application Software. Temporal Program Flow Monitoring consists of the mechanisms Deadline Supervision and Alive Supervision, which will be discussed thereafter.

The Watchdog Manager also provides a mechanism called Logical Supervision, which can be combined with Deadline Supervision to provide a high diagnostic coverage. This topic is discussed in Chapter 2.3.

Also, an overview of the Timing Protection mechanisms of AUTOSAR OS will be given.

#### 2.2.2.1 Supervised Entities

The Watchdog Manager supervises the execution of Application Software in an AUTOSAR ECU. The logical units of supervision are called Supervised Entities. There is no fixed relationship between Supervised Entities and the architectural building blocks in AUTOSAR. Typically a Supervised Entity may represent one SW-Cs or a Runnable within an SW-C, a BSW module or CDD depending on the choice of the developer.

Important places in a Supervised Entity are defined as Checkpoints. The code of Supervised Entities is interlaced with function calls of the Watchdog Manager. Those calls are used to report to the Watchdog Manager that a Checkpoint is reached.

#### 2.2.2.2 Watchdog Manager

The Watchdog Manager is a basic software module of the AUTOSAR Architecture.

The Watchdog Manager links the triggering of the Watchdog Hardware<sup>20</sup> to the supervision of software execution. When a violation of the configured temporal and/or logical constraints on program execution is detected, a number of configurable actions to recover from this failure will be taken.

The Watchdog Manager provides the following mechanisms for Temporal Program Flow Monitoring:

Alive Supervision: Periodic Supervised Entities have constraints on the frequency with which they are executed. By means of Alive Supervision, Watchdog Manager checks periodically if the Checkpoints of a Supervised Entity have been reached within the given limits. This means that Watchdog Manager checks if a Supervised Entity is run not too frequently or not too rarely.

$<sup>^{20}</sup>$  See Layered Software Architecture, V3.4.0, R4.1 Rev 3, Page 42, Page 82.

AUTOSAR Release 4.2.2

Alive Supervision is performed using a single Checkpoint without transitions. The supervised Entity must cyclically call the Checkpoint to signal its timely operation. The Watchdog Manager is executed periodically by the Operating System to verify the Checkpoint parameters.

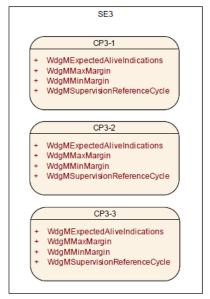

A Supervised Entity can also be monitored by multiple instances of Alive Supervision, therefore containing an independent checkpoint per Alive Supervision. Please see Figure 9.

Figure 9: Alive Supervision with independent Checkpoints<sup>21</sup>

Deadline Supervision: Aperiodic or episodic Supervised Entities have individual constraints on the timing between two Checkpoints. By means of Deadline Supervision, the Watchdog Manager checks the timing of transitions between two Checkpoints of a Supervised Entity. This means that the Watchdog Manager checks if some steps in a Supervised Entity take a time that is within the configured minimum and maximum. Please see Figure 10.

If the second Checkpoint is never reached, then Deadline Supervision will fail to detect this issue. This issue appears because the timing checks are performed by the Watchdog Manager after the second Checkpoint is called.

Figure 10: Deadline Supervision<sup>22</sup>

26 of 71

<sup>&</sup>lt;sup>21</sup> Specification of Watchdog Manager, V2.5.0, R4.1 Rev 3, Page 43, Chapter 7.1.5 Alive Supervision Functions

# Overview of Functional Safety Measures in AUTOSAR AUTOSAR Release 4.2.2

#### 2.2.2.3 Timing Protection of the Operating System

According to the AUTOSAR OS Specification, a timing fault in a real-time system occurs when a task or interrupt misses its deadline at runtime.<sup>23</sup>

The AUTOSAR OS does not offer deadline supervision for timing protection. Deadline supervision is insufficient to correctly identify the Task or Interrupt causing a timing fault in an AUTOSAR system. A deadline violation may be caused by unrelated Tasks or Interrupts interfering with the execution. Please consult the AUTOSAR OS Specification<sup>23</sup> for further details.

Whether a task or interrupt meets its deadline in a fixed priority preemptive operating system like AUTOSAR OS is determined by the following factors:

- The execution time of Task/Interrupt in the system.

- The blocking time that Task/Interrupt suffers from lower priority Tasks/Interrupts locking shared resources or disabling interrupts.

- The inter-arrival rate of Task/Interrupt in the system.

For safe and accurate timing protection it is necessary for the operating system to control these factors at runtime to ensure that Tasks/Interrupts can meet their respective deadlines. The AUTOSAR OS provides the following timing protection mechanisms:

- Execution Time Protection. An upper bound for execution time of Tasks or Cat2<sup>24</sup>

Interrupts, the so called Execution Budget, is monitored via the OS to prevent

timing errors.

- 2. Locking Time Protection. An upper bound for blocking of resources, locking and suspending of interrupts, the so called Lock Budget, is monitored by the OS.

- 3. Inter-Arrival Time Protection. A lower bound between tasks being activated or Cat 2 Interrupts arriving, a so called Time Frame, is monitored via the OS to prevent timing errors.

Note: Execution time enforcement requires hardware support, e.g. a timing enforcement interrupt. If an interrupt is used to implement the time enforcement, the priority of this interrupt shall be high enough to "interrupt" the supervised tasks or interrupts.

27 of 71

Specification of Watchdog Manager, V2.5.0, R4.1 Rev 3, Page 61, Chapter 7.3 Watchdog Handling

Specification of Operating System, V5.3.0 R4.1 Rev 3, Chapter 7.7.2

<sup>&</sup>lt;sup>24</sup> Category 2 Interrupts are managed by the Operating System. Category 1 Interrupts are executed outside of the Operating System and therefore cannot be monitored.

#### 2.2.3 Detection and Reaction

The Watchdog Manager provides three mechanisms for Temporal and Logical Program Flow Monitoring: Deadline Supervision, Alive Supervision and Logical Supervision.

The supervision mechanisms are configured statically. For the monitoring of a Supervised Entity, more than one supervision mechanism can be employed.

Based on the results from each of enabled mechanisms, the status of the Supervised Entity (called Local Status) is computed. When the status of each Supervised Entity is determined, then based on each Local Supervision Status, the status of the whole MCU is determined (called Global Supervision Status).

Depending on the Local Supervision Status of each Supervised Entity and on the Global Supervision Status, the Watchdog Manager initiates a number of mechanisms to recover from supervision failures. These range from local error recovery within the Supervised Entity to a global reset of the ECU.

The following error recovery mechanisms can be employed by the Watchdog Manager:

#### 1. Error Handling in the Supervised Entity

In case the Supervised Entity is an SW-C or a CDD, then the Watchdog Manager may inform the Supervised Entity about supervision failures via the RTE Mode mechanism. The Supervised Entity may then take its actions to recover from that failure.

The Watchdog Manager may register an entry with the Diagnostic Event Manager (DEM) when it detects a supervision failure. A Supervised Entity may take recovery actions based on that error entry.

#### 2. Partition Shutdown

If the Watchdog Manager module detects a supervision failure in a *Supervised Entity* which is located in a non-trusted partition, the Watchdog Manager module may request a partition shutdown by calling the BswM.

#### 3. Reset by Hardware Watchdog

The Watchdog Manager indicates to the Watchdog Interface when Watchdog Interface shall no longer trigger the hardware watchdog. After the timeout of the hardware watchdog, the hardware watchdog resets the ECU or the MCU. This leads to a re-initialization of the ECU and/or MCU hardware and the complete re-initialization of software.

#### 4. Immediate MCU Reset

In case an immediate, global reaction to the supervision failure is necessary, the Watchdog Manager may directly cause an MCU reset. This will lead to a reinitialization of the MCU hardware and the complete software. Usually, a MCU reset will not re-initialize the rest of the ECU hardware.

Note: The AUTOSAR Document "Explanation of Error Handling on Application Level" provides additional information on error handling. Within the document it is explained how error handling can be performed and where the required data (e.g. substitute values) can be obtained from. Furthermore the document provides a detailed explanation (user's manual) on how OS-Application/Partition termination and restart in AUTOSAR is performed.

#### 2.2.4 Limitations

**AUT** SAR

- 1. The granularity of Checkpoints is not fixed by the Watchdog Manager. Few coarse-grained Checkpoints limit the detection abilities of the Watchdog Manager. For example, if an application SW-C only has one Checkpoint that indicates that a cyclic Runnable has been started, then the Watchdog Manager is only capable of detecting that this Runnable is re-started and check the timing constraints. In contrast, if that SW-C has Checkpoints at each block and branch in the Runnable the Watchdog Manager may also detect failures in the control flow of that SW-C. High granularity of Checkpoints causes a complex and large configuration of the Watchdog Manager.

- 2. The Deadline Supervision has a weakness: it only detects the delays (when the End Checkpoint is reported), but it does not detect the timeouts (when the End Checkpoint is not reported at all).

- 3. The nesting of Deadline Supervision (i.e. start 1, start 2, end 2, end 1) is not supported.

- 4. The Alive Supervision function with more than one checkpoint per Supervised Entity is not consistently specified within the Specification of Watchdog Manager document. For now it is recommended to support only one alive supervision checkpoint per Supervision Entity.

- 5. In order to shutdown or restart (as error reaction) a partition containing Supervised Entities, the integrator code (OS Application's restart task) must deactivate (or deactivate + activate) all Supervised Entities of the involved partition, by calling available functions of Watchdog Manager. This is a bit complex, in future releases of the Specification of Watchdog Manager document it is considered to add a new function of Watchdog Manager for this.

- 6. Libraries cannot call BSWs, so libraries cannot be supervised by Watchdog Manager. Deadline Supervision could be used however by placing checkpoints before and after a library call in the module's code to supervise libraries.

- 7. It is not standardized how BSW modules are identified with Supervised Entity IDs.

\_

#### 2.2.5 References to AUTOSAR Documents

**Source:** Requirements on AUTOSAR Features, V1.2.1, R4.1 Rev 2

# [RS\_BRF\_00131] AUTOSAR shall support program flow monitoring

| Туре:                | Valid                                                                                                                                                                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description:         | AUTOSAR shall support logical and temporal program flow monitoring to detect if program flow control is violated. AUTOSAR shall offer support for ensuring that the program flow monitoring mechanisms are working properly                                                     |

| Rationale:           | Using flow control to detect if a software components runs wild is an established safety feature Using program flow control to detect if a runnable (or a sequence of runnables) is executed out of order or not at all is a well established safety feature                    |

| Use Case:            | To detect a defective program sequence. A defective program sequence exists, if the individual elements of a program (for example, software modules, subprograms or commands) are processed in the wrong sequence or period of time, or if the clock of the processor is faulty |

| Dependencies:        |                                                                                                                                                                                                                                                                                 |

| Supporting Material: | ISO 26262-5:2011 Annex D, ISO 26262-6:2011                                                                                                                                                                                                                                      |

J (RS\_Main\_00010)

# [RS\_BRF\_02056] AUTOSAR OS shall support timing protection

| Valid                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If configured, AUTOSAR OS shall support to supervise runtime of tasks and interrupts, together with frequency of task and interrupt activation, to detect and react if a task or an interrupt consume more runtime than configured |

| Systems are usually evaluated based on assumptions concerning runtime and frequency of tasks and interrupts. The violation of these assumptions may lead to the violation of the safety goals                                      |

| Stop application parts which violate runtime constraints                                                                                                                                                                           |

|                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                    |

J (RS\_Main\_00010)

#### **AUTOSAR Release 4.2.2**

### [RS\_BRF\_01224] AUTOSAR OS shall support timing protection

| Type:                | Valid                                                            |

|----------------------|------------------------------------------------------------------|

| Description:         | AUTOSAR OS shall offer functionality to limit runtime and        |

|                      | activation frequency of tasks and interrupts                     |

| Rationale:           | This is a pre-requirement to catch problems with interrupt lines |

|                      | (babbling idiot) and certain programming bugs                    |

| Use Case:            | Disable an interrupt line if this interrupt line fires too often |

| Dependencies:        |                                                                  |

| Supporting Material: |                                                                  |

J (RS\_Main\_00100)

#### 2.2.6 References to ISO26262

The following references to the ISO26262 standard are related to the aspects of freedom from interference for software components with different ASIL ratings. Concepts related to timing supervision are covered.

| ID | ISO26262 Reference           |

|----|------------------------------|

| 03 | Part 6: [D.2.1]              |

| 08 | Part 6: [D.2.2]              |

| 09 | Part 6: [7.4.14] Table 4: 1d |

**Table 5: ISO26262 Timing Monitoring References**

### 2.3 Logical Supervision

Logical Supervision is a technique for checking the correct execution of software and focuses on control flow errors.

Control flow errors cause a divergence from the valid (i.e. coded/compiled) program sequence during the error-free execution of the application. An incorrect control flow occurs if one or more program instructions are processed either in the incorrect sequence or are not even processed at all. Control flow errors can for example lead to data inconsistencies, data corruption, or other software failures.

#### 2.3.1 Fault Models

According to ISO 26262<sup>26</sup>, the following Timing- and Execution-related faults can be considered as a cause for interference between software components:

- Blocking of execution

- Deadlocks

- Livelocks

- Incorrect allocation of execution time

- Incorrect synchronization between software elements

Logical and temporal monitoring of program sequences is used in the automotive industry and mentioned e.g. in ISO 26262 as a measure to detect failures of the processing units (i.e. CPU, microcontroller) and as measure for the detection of failures of the HW clock.

Faults in execution of program sequences (i.e. invalid execution of program sequences) can lead to data corruption, process crashes, or fail-silence violations. Logical monitoring of program sequences is required/recommended/proposed by ISO 26262, IEC 61508, MISRA.

#### 2.3.2 Description

Logical Supervision of the execution sequence of a program enables the detection of errors that cause a divergence from the valid program sequence during the error-free execution of the application. An incorrect program flow occurs if one or more program instructions are processed either in an incorrect sequence or not even processed at all.

The Watchdog Manager supervises the execution of Application Software in an AUTOSAR ECU. The logical units of supervision are called Supervised Entities. There is no fixed relationship between Supervised Entities and the architectural building blocks in AUTOSAR. Typically a Supervised Entity may represent one SW-Cs or a Runnable within an SW-C, a BSW module or CDD depending on the choice of the developer.

-

<sup>&</sup>lt;sup>26</sup> [ISO 26262-6, Annex D] D.2.2 Timing and execution

**AUTOSAR Release 4.2.2**

Places relevant for logical supervision in a Supervised Entity are defined as Checkpoints. The code of Supervised Entities is interlaced with function calls of the Watchdog Manager. Those calls are used to report to the Watchdog Manager that a Checkpoint is reached.

Each Supervised Entity has one or more Checkpoints. The Checkpoints and Transitions between the Checkpoints of a Supervised Entity form a Graph.

A Graph may have one or more<sup>27</sup> initial Checkpoints and one or more final Checkpoints. Any sequence of starting with any initial checkpoint and finishing with any final checkpoint is correct, assuming that the checkpoints belong to the same Graph.

A graph within a Supervised Entity is called an Internal Graph. Checkpoints from different Supervised Entities can be connected by External Transitions, forming an External Graph.

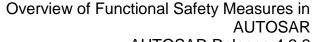

Figure 11 shows a Graph representation of a While-Loop, which consists of Checkpoints and Transitions.

Figure 11: Abstract Control Flow Graph of a While-Loop<sup>28</sup>

At runtime, the Watchdog Manager verifies if the supervised Entities are executed according to the configured Graphs. This is called Logical Supervision.

Also, the Watchdog Manager can verify the timing of Checkpoints and Transitions within a Graph.

The timing of Transitions between Checkpoints can be verified via Deadline Supervision, whereas Logical Monitoring verifies the correct order of the Checkpoints. The details of Timing Monitoring mechanisms are described in Chapter 2.2.

<sup>&</sup>lt;sup>27</sup> Internal graphs can have only one initial Checkpoint. External graphs can have multiple initial Checkpoints.

Specification of Watchdog Manager, V2.5.0, R4.1 Rev 3, Chapter 7.1.7 Logical Supervision

Document ID 664: AUTOSAR\_TR\_OverviewOfFunctionalSafetyMeasuresInAUTOSAR

- AUTOSAR confidential -

#### 2.3.3 Detection and Reaction

During design phase the valid program sequences are identified and modeled. During runtime the Watchdog Manager uses this model to supervise or monitor the proper execution of program sequences.

The Watchdog Manager provides three mechanisms for Temporal and Logical Program Flow Monitoring: Deadline Supervision, Alive Supervision and Logical Supervision.

The supervision mechanisms are configured statically. For the monitoring of a Supervised Entity, more than one supervision mechanism can be employed.

Based on the results from each of enabled mechanisms, the status of the Supervised Entity (called Local Status) is computed. When the status of each Supervised Entity is determined, then based on each Local Supervision Status, the status of the whole MCU is determined (called Global Supervision Status).

Depending on the Local Supervision Status of each Supervised Entity and on the Global Supervision Status, the Watchdog Manager initiates a number of mechanisms to recover from supervision failures. These range from local error recovery within the Supervised Entity to a global reset of the ECU.

The following error recovery mechanisms can be employed:

#### 1. Error Handling in the Supervised Entity:

In case the Supervised Entity is an SW-C or a CDD, then the Watchdog Manager may inform the Supervised Entity about supervision failures via the RTE Mode mechanism. The Supervised Entity may then take its actions to recover from that failure.

The Watchdog Manager may register an entry with the Diagnostic Event Manager (DEM) when it detects a supervision failure. A Supervised Entity may take recovery actions based on that error entry.

#### 2. Partition Shutdown

If the Watchdog Manager module detects a supervision failure in a *Supervised Entity* which is located in a non-trusted partition, the Watchdog Manager module may request a partition shutdown by calling the BswM.

#### 3. Reset by Hardware Watchdog

The Watchdog Manager indicates to the Watchdog Interface when Watchdog Interface shall no longer trigger the hardware watchdog. After the timeout of the hardware watchdog, the hardware watchdog resets the ECU or the MCU. This leads to a re-initialization of the ECU and/or MCU hardware and the complete re-initialization of software.

# Overview of Functional Safety Measures in AUTOSAR AUTOSAR Release 4.2.2

#### AUTUSAK Release 4.2.

#### 4. Immediate MCU Reset

In case an immediate, global reaction to the supervision failure is necessary, the Watchdog Manager may directly cause an MCU reset. This will lead to a reinitialization of the MCU hardware and the complete software.

Note: The AUTOSAR Document "Explanation of Error Handling on Application Level" provides additional information on error handling. Within the document it is explained how error handling can be performed and where the required data (e.g. substitute values) can be obtained from. Furthermore the document provides a detailed explanation (user's manual) on how OS-Application/Partition termination and restart in AUTOSAR is performed.

#### 2.3.4 Limitations

- 1. For Logical Supervision, Watchdog manager does not support any overlapping graphs a checkpoint shall belong to maximum one Graph. This is required to be able to allocate a received Checkpoint notification to a Graph.

- 2. Watchdog Manager does not support Logical Supervision of concurrently executed Supervised Entities, because it follows only one instance of a Graph at a time.

- 3. In order to shutdown or restart (as error reaction) a partition containing Supervised Entities, the integrator code (OS Application's restart task) must deactivate (or deactivate + activate) all Supervised Entities of the involved partition, by calling available functions of Watchdog Manager.

\_

#### 2.3.5 References to AUTOSAR Documents

Source: Requirements on AUTOSAR Features, V1.2.1, R4.1 Rev 2

## [RS\_BRF\_00131] AUTOSAR shall support program flow monitoring

| 1                    |                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:                | Valid                                                                                                                                                                                                                                                                           |

| Description:         | AUTOSAR shall support logical and temporal program flow monitoring to detect if program flow control is violated. AUTOSAR shall offer support for ensuring that the program flow monitoring mechanisms are working properly                                                     |

| Rationale:           | Using flow control to detect if a software components runs wild is an established safety feature Using program flow control to detect if a runnable (or a sequence of runnables) is executed out of order or not at all is a well established safety feature                    |

| Use Case:            | To detect a defective program sequence. A defective program sequence exists, if the individual elements of a program (for example, software modules, subprograms or commands) are processed in the wrong sequence or period of time, or if the clock of the processor is faulty |

| Dependencies:        | <b></b>                                                                                                                                                                                                                                                                         |

| Supporting Material: | ISO 26262-5:2011 Annex D, ISO 26262-6:2011                                                                                                                                                                                                                                      |

| (RS\_Main\_00010)

#### 2.3.6 References to ISO26262

The following references to the ISO26262 standard are related to the aspects of freedom from interference for software components with different ASIL ratings. Concepts related to logical supervision are covered.

| ID | ISO26262 Reference               |

|----|----------------------------------|

| 03 | Part 6: [D.2.1]                  |

| 08 | Part 6: [D.2.2]                  |

| 09 | Part 6: [7.4.14] Table 4: 1d. 1e |

Table 6: ISO26262 Logical Supervision References

#### 2.4 End-2-End Protection

In a distributed system, the exchange of data between a sender and the receiver(s) can affect functional safety, if its safe behavior safety depends on the integrity of such data (see "Exchange of Information" fault example in the beginning of this chapter). Therefore, such data shall be transmitted using mechanisms to protect it against the effects of faults within the communication link.

## 2.4.1 Fault Models

According to ISO 26262<sup>30</sup>, the following Exchange of Information-related faults can be considered for each sender or each receiver software component executed in different software partitions or ECUs:

- · Repetition of information;

- Loss of information;

- Delay of information;

- Insertion of information;

- Masquerade or incorrect addressing of information;

- Incorrect sequence of information;

- Corruption of information;

- Asymmetric information sent from a sender to multiple receivers;

- Information from a sender received by only a subset of the receivers;

- Blocking access to a communication channel.

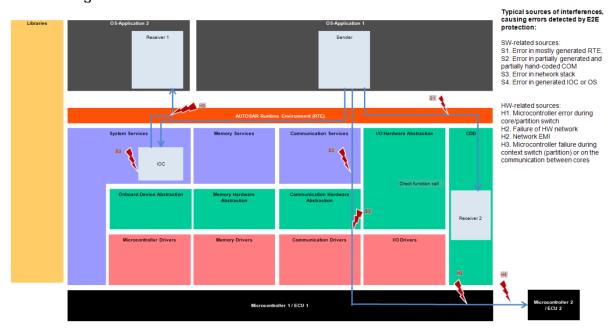

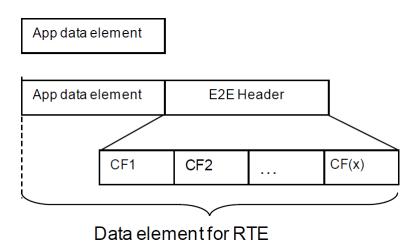

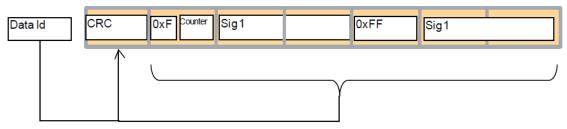

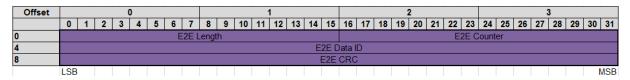

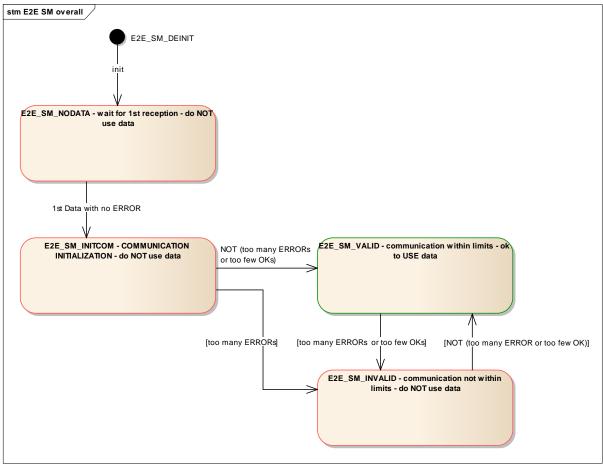

Figure 12: End-2-End Protection<sup>31</sup>

<sup>31</sup> Specification of SW-C End-to-End Communication Protection Library, V3.2.1, R4.1 Rev 3

<sup>&</sup>lt;sup>30</sup> [ISO 26262-6, Annex D] D.2.4 Exchange of Information

The concept of End-2-End protection assumes that safety-related data exchange shall be protected at runtime against the effects of faults within the communication link (see Figure 12). Examples for such faults are random HW faults (e.g. corrupt registers of a CAN transceiver), interference (e.g. due to EMC), systematic faults within the software implementing the VFB communication (e.g. RTE, IOC, COM and network stacks) inside the ECU and outside, such as on Gateways.

The following faults related to message exchange via communication network have been considered in the End-2-End Library.

| Fault Model               | Description                                                                           |

|---------------------------|---------------------------------------------------------------------------------------|

| Repetition of             | A type of communication fault, were information is received                           |

| information               | more than once.                                                                       |

| Loss of                   | A type of communication fault, were information or parts of                           |

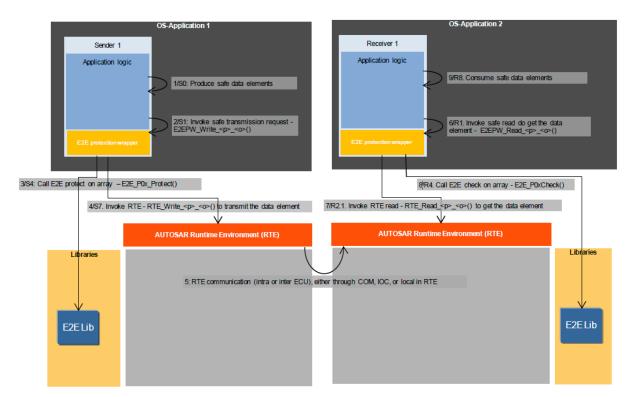

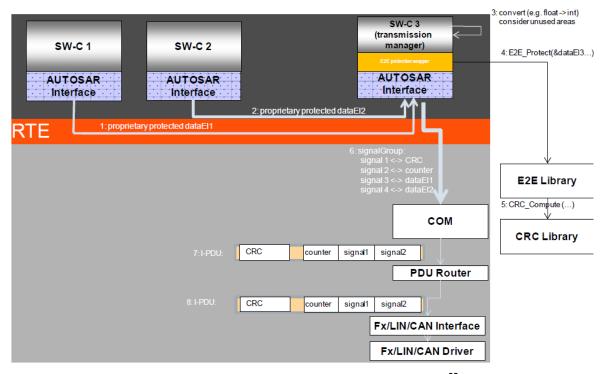

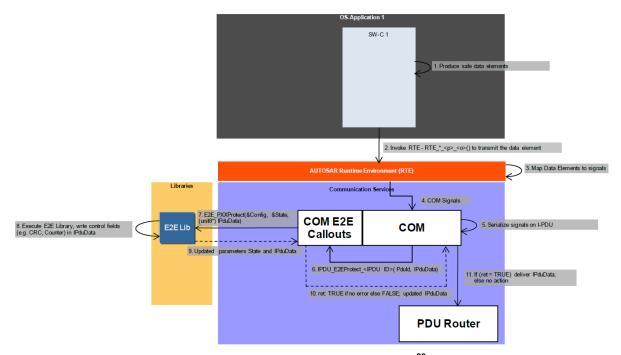

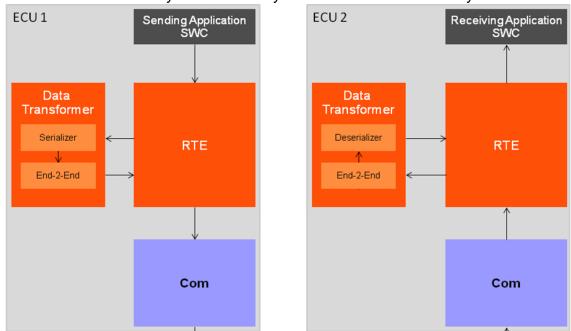

| information               | information are removed from a stream of transmitted                                  |